be combined with additional Verilog code. To do it, the Verilog code for N-bit Adder uses Generate Statement in Verilog to create a chain of full adders for implementing the N-bit Adder. example is a half or a full adder block with the the well known input and output signals. Our textbook is Computer Organization and Design by Hennessy and Patterson.

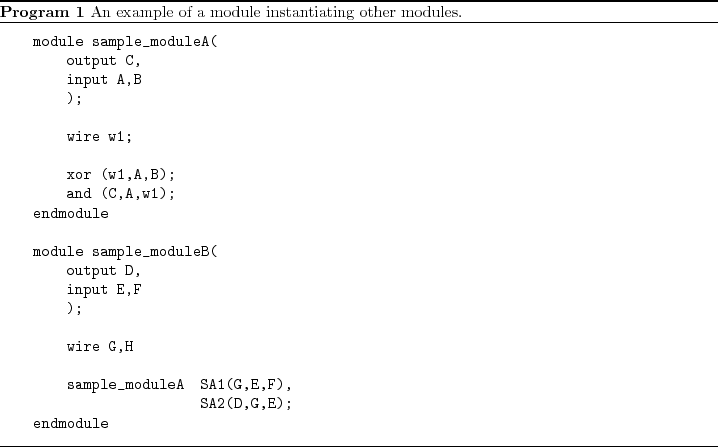

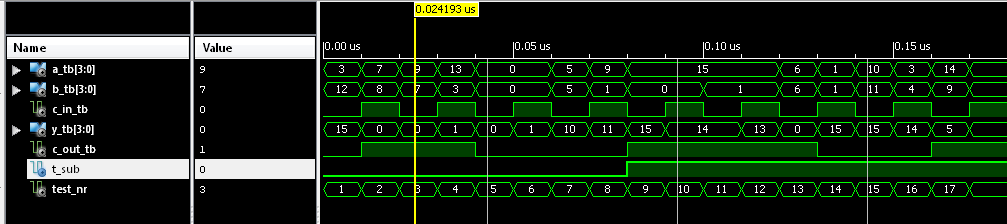

I welcome any suggestions, however minor, for improving this code, which runs at EDA Playground. The full adder is a digital component that performs three numbers an implemented using the logic gates. I am stuck and not sure what next to look at to correct this error.Īny advice in what next steps (or some pointers) to be checked in order to rectify this would be helpful. The Verilog code for N-bit Adder is designed so that the N value can be initialized independently for each instantiation. I'll be teaching Computer Architecture at the undergraduate level this fall and want to make sure that my example Verilog code follows best practices. Behaviouralmodel modulehalfaddstr(sum,carry,a,b) modulehalfadddf(sum. E.g. There are no compile errors, but at the output (Waveform), I get Z and X for Sum and Carry. Bottom-Up Methodology: In this approach, we first identify small blocks that are available to us and use them to construct a big block. I have been designing a basic full adder with two half adder modules and trying to test it with a testbench.

0 kommentar(er)

0 kommentar(er)